# Reprinted from

# **REGULAR PAPER**

New Model of Defect Formation Caused by Retainer Ring in Chemical Mechanical Polishing

Akira Isobe, Takashi Komiyama, and Syuhei Kurokawa

Jpn. J. Appl. Phys. 52 (2013) 126502

http://dx.doi.org/10.7567/JJAP.52.126502

# New Model of Defect Formation Caused by Retainer Ring in Chemical Mechanical Polishing

Akira Isobe<sup>1\*</sup>, Takashi Komiyama<sup>2</sup>, and Syuhei Kurokawa<sup>1</sup>

E-mail: iso6016@yahoo.co.jp

Received April 7, 2013; revised July 17, 2013; accepted August 29, 2013; published online November 14, 2013

Defect formation by retainer ring pressure in chemical mechanical polishing (CMP) was investigated. It was found that a higher retainer ring pressure causes more defects. The mechanism underlying this finding was considered to be the agglomeration of abrasive particles mixed with polished polymers from the retainer ring. Such agglomeration is accelerated by increasing the retainer ring pressure. This ring pressure exerts stress onto particles and also polishes the polymers from the ring. Lowering the retainer ring pressure and also changing the ring material from polymers, which are easy to polish, to tough materials are effective for minimizing the density of defects in CMP.

© 2013 The Japan Society of Applied Physics

#### 1. Introduction

Chemical mechanical polishing (CMP) is widely used and one of the most important processes in semiconductor device manufacturing. 1-6) In the CMP process, a wafer is held on a rotating polishing head, a polishing pad is placed on a rotating platen, slurry is supplied on the pad, and the wafer is pressed on the polishing pad. The polishing depends on the wafer pressure and the relative speed between the wafer and the polishing pad. The relationship between the material removal rate and the polishing pressure as well as the relative speed is known as Preston's equation.<sup>8)</sup> The relative speed is easily controlled because it is determined simply by the geometrical parameters and rotational speeds of the wafer and the polishing pad. In the contrast, the pressure, particularly the within-wafer pressure uniformity, is difficult to control but is a key in CMP. Therefore, various developments in the polishing head have taken place. In the past, when CMP was introduced in LSI manufacturing, the polishing head structure was very simple. There were a flat plate with a backing film to hold a wafer and a retainer ring with its surface designed to be lower than the wafer surface so as not to come into contact with the polishing pad. <sup>9)</sup> The pressure distribution within the wafer was affected by the backing film properties and there was a limitation in the uniformity improvement using this structure. Then, an "airbag"-type head began to be applied because of the better within-wafer uniformity. 10) This type of head consists of a membrane air bag and a retainer ring. It can realize very uniform polishing pressure based on Pascal's principle. The pressure is applied by pressurized air introduced into the air bag and the pressure is constant on the entire membrane. This head also needs a retainer ring, which must be in contact with the pad surface during polishing, differently from the backing-film-type head. The relative position of the wafer and ring was fixed for the backing film type but not fixed for the air bag type. Therefore, the ring cannot hold the wafer if it does not come in contact with the pad. Thus, the ring position is secured by adding positive pressure to the ring. This head structure can also control the wafer edge profile.<sup>11)</sup> The wafer edge tends to have irregular pressure distribution<sup>12)</sup> because of the strong contact of the wafer with the pad at the edge. The retainer ring is also used to prevent this problem. By controlling the retainer ring pressure, the pressure distribution at the wafer edge can be optimized so that the removal rate (RR) profile can also be optimized. For these reasons, the air-bag-type head has become very popular because of its capability of achieving excellent uniformity.

On the other hand, as device nodes progress and the number of applications of CMP in semiconductor device manufacturing increases, defect control is becoming another key factor in CMP.<sup>13–15)</sup> From this viewpoint, the development of a low-*k* Cu interconnect process is a challenge because low-*k* films<sup>16,17)</sup> are fragile and easily peel off especially at the wafer edge portion.<sup>18)</sup> Therefore, wafer edge pressure control by adjusting the retainer ring pressure is also considered important for preventing low-*k* film delamination.

Microscratches, which are well-known defects in CMP, <sup>19,20)</sup> may also be affected by the retainer ring pressure. Microscratches are considered to be caused by large particles in a slurry and various efforts to reduce the microscratch counts have been made such as monitoring the slurry quality by measuring the large-particle count (LPC) or large-particle rejection using a point-of-use (POU) filter. <sup>21–23)</sup> Recently, however, it has been considered that large particles in the slurry itself are not the source of microscratches but rather large particles grown in the slurry distribution system or during polishing on a polishing pad. <sup>24–26)</sup> The growth of such particles is caused by the stress between the wafer and the pad during polishing. Thus, the pressure between the pad and the retainer ring may also affect the microscratch count.

The effect of the retainer ring pressure on CMP defects is studied in this paper. In addition, the effect of the retainer ring material is also evaluated. From these experimental results, the mechanism of large-particle generation during polishing is discussed.

# 2. Experimental Procedure

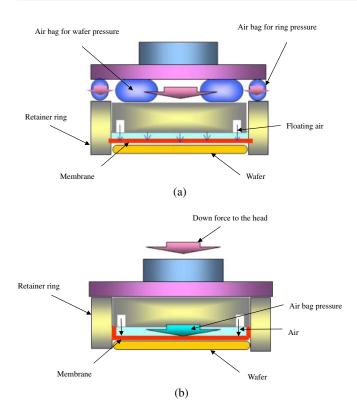

ChaMP-222, a CMP tool from Accretech, was used for the evaluation. The head structure of this tool is compared with the structure of a conventional air-bag-type head in Fig. 1.<sup>27)</sup> The conventional air-bag-type head controls the retainer ring pressure by changing the head down force. As shown in Fig. 1(b), the total force acting on both the wafer and the ring is also applied to the head. The wafer pressure is controlled by adjusting the air pressure to the air bag. The ring pressure is determined by the difference between the

<sup>&</sup>lt;sup>1</sup>Kyushu University, Fukuoka 819-0395, Japan

<sup>&</sup>lt;sup>2</sup>Tokyo Seimitsu Co., Ltd., Hachioji, Tokyo 192-0032, Japan

**Fig. 1.** (Color online) Polishing head structures: (a) air floating head (ChaMP-222) and (b) conventional air bag head.

total force and wafer down force. Since the area of the ring is smaller than that of the wafer, "pressure" control for the ring cannot be as accurate as that for the wafer. Theoretically, the ring pressure can be below the wafer pressure, but it is recommended that it be set higher than the wafer pressure to avoid the risk of wafer slippage caused by negative ring pressure, by varying the head down force and air bag pressure. In contrast, ChaMP-222 has a unique head structure, as shown in Fig. 1(a), which can control the wafer pressure and ring pressure separately. The head is positioned close to the polishing pad surface, and pressures are applied independently to the wafer and the ring. With this structure, the ring pressure can be controlled precisely without losing the benefit of the excellent uniformity of the air-bag-type head. This head can control the ring pressure to be below the wafer pressure.

#### 2.1 Experiment 1

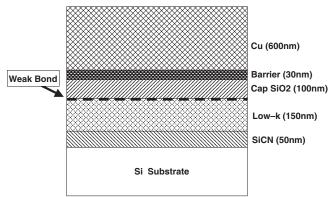

A low-*k* Cu structure on a 200 mm wafer was evaluated. The film structure consists of a 600 nm layer of Cu on top, 30 nm Ta as the barrier metal and 100 nm of cap SiO<sub>2</sub> on 150 nm of CVD-deposited low-*k* film, as shown in Fig. 2. Plasma treatment to enhance the adhesion between the low-*k* film and the cap SiO<sub>2</sub> film is usually performed before cap SiO<sub>2</sub> deposition, <sup>28,29</sup> which was omitted in this experiment to accelerate delamination failure. Defect evaluation was carried out using the defect inspection tool LS6700 from Hitachi High-Tech. The defect mode was confirmed by optical microscopy and scanning electron microscopy (SEM). The polishing conditions for this evaluation were as follows. For the Cu polishing step, the wafer pressure was 20.7 kPa, the platen rotational speed was 83 min<sup>-1</sup>, the wafer rotational speed was 78 min<sup>-1</sup>, and the ring pressure was

Fig. 2. Film structure evaluated in experiment 1.

varied from 10.3 to 41.4 kPa. The slurry was commercially available  $\rm H_2O_2$ -based colloidal silica slurry and the polishing pad was IC1400 with k-grooves from Nitta Haas. For the barrier-polishing step, the wafer pressure was 17.2 kPa, the platen rotational speed was  $83\,\rm min^{-1}$ , the wafer rotational speed was  $78\,\rm min^{-1}$ , and the ring pressure was  $10.3\,\rm kPa$ . The slurry was commercially available  $\rm H_2O_2$ -based colloidal silica slurry and the polishing pad was IC1400 with k-grooves.

#### 2.2 Experiment 2

A blanket TEOS film on a 200 mm wafer was polished. The same CMP tool as that used in experiment 1 was used and the supplied slurry was twofold-diluted SS25 from Cabot. The polishing pad was IC1000 with A21 XY-grooves. The wafer pressure was 20.7 kPa, the platen rotational speed was 90 min<sup>-1</sup>, the wafer rotational speed was 90 min<sup>-1</sup>, and the ring pressure ranged from 6.9 to 41.4 kPa. The slurry was supplied with and without a POU filter. The filter was 3 µm Millipore Solaris (10 in.). The post CMP cleaning conditions are as follows: brush cleaning with 1% NH<sub>4</sub>OH for 20 s and with DIW for 20 s in the brush 1 chamber; brush cleaning with 0.5% DHF for 20 s and rinsing with DIW for 20 s in the brush 2 chamber; chemical spin etching with 0.5% DHF for 10 s and rinsing with DIW for 30 s in the chemical chamber; and megasonication in DIW for 15 s, rinsing with DIW for 20 s, and spin drying with  $N_2$  for 12 s in the spin dry chamber. Defect evaluation was performed using LS6700. Defects were automatically categorized into particles and scratches by the equipment.

#### 2.3 Experiment 3

The standard material for the ring was poly(ether ether ketone) (PEEK) in Experiments 1 and 2. Two other rings made of poly(phenylene sulfide) (PPS) and poly(butylene naphthalate) (PBN) were evaluated to determine the effect of the material. PPS is widely used as a ring material in popular CMP tools. PBN was expected to show a lower wear rate than PEEK. The polishing tool, slurry, and pad are the same as those used in Experiment 2. The polishing conditions are also the same as those used in Experiment 2 except that ring pressure was fixed to 20.7 kPa and a POU filter was not applied.

The wear rates of the ring materials were evaluated. Specimens with dimensions of  $15 \times 15 \times 2 \text{ mm}^3$  were

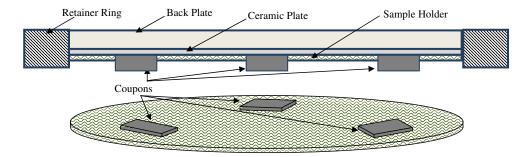

Fig. 3. (Color online) Illustration of sample holder for retainer ring material coupons.

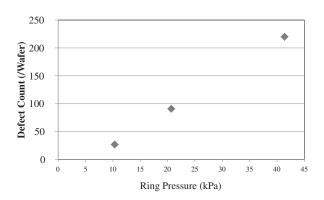

Fig. 4. Defect count vs ring pressure for Cu CMP.

prepared from the evaluated materials. A jig for a 200 mm wafer head was fabricated to hold three specimens as shown in Fig. 3. Three specimens from the same material were attached to the jig, and their change in thickness was measured to evaluate the material wear rate. The same CMP tool, ChaMP-222, was used and a wafer pressure of 6.9 kPa was applied. This pressure is calculated to be 337.8 kPa for the size of the specimens. The pad and head rotational speed was 30 min<sup>-1</sup>. The polishing time was 30 min. Polishing was repeated 4 times for each set of specimens. Two sets of tests were performed for each material and the average of 24 data sets of thickness changes was used as the wear rate.

#### 3. Results and Discussion

## 3.1 Experiment 1

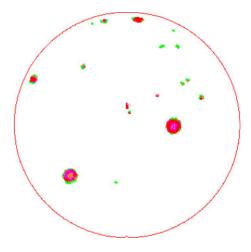

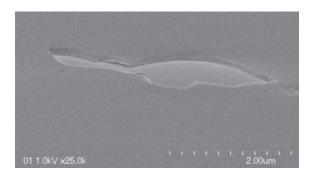

Figure 4 shows a plot of the defect count vs retainer ring pressure. It shows a very strong correlation between the defect count and ring pressure. A higher ring pressure results in a higher defect count. Figure 5 shows the defect distribution in the wafer and Fig. 6 shows a SEM image of a typical defect on the wafer. It was confirmed that delamination occurred between the low-k and cap SiO<sub>2</sub> films. The distribution of the defects was random within the wafer and was not concentrated at the wafer edge. Delamination defects are considered to be caused by stress concentration, and the wafer edge is considered to be the region where the stress concentrates. However, the result indicates that delamination at the wafer edge is not the main source of the defects. A higher defect count at a higher ring pressure also indicates that the wafer edge pressure distribution is not the key for the delamination because a higher ring pressure should result in a lower wafer edge pressure.

Fig. 5. (Color online) Distribution of defects after Cu/low-k CMP.

Fig. 6. SEM image of a defect.

#### 3.2 Experiment 2

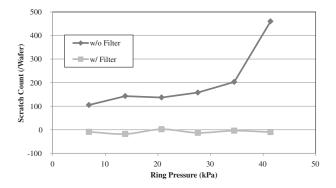

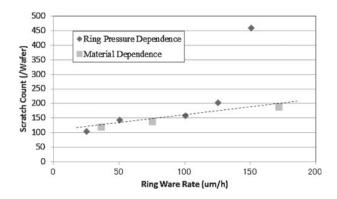

Figure 7 shows the microscratch count on the  $SiO_2$  film against ring pressure. The scratch count remains almost zero regardless of the ring pressure when a POU filter is applied. A negative scratch count is due to a noise because the count is calculated from the difference between the counts before and after the polishing. In the case without a POU filter, the scratch count increases with the ring pressure. It is considered that large-particle growth is caused by the stress induced by the ring pressure, or that the polished material from the ring becomes the source of the scratches.

#### 3.3 Experiment 3

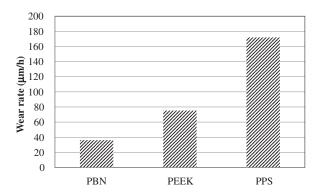

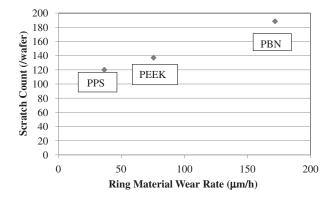

Figure 8 shows the material wear rates. PPS has the highest

Fig. 7. Microscratch count vs retainer ring pressure.

Fig. 8. Wear rates of ring materials.

**Fig. 9.** Microscratch count dependence on wear rate for different ring materials.

rate and PBN has the lowest rate. The scratch count was plotted against the material wear rate, as shown in Fig. 9.

A higher-wear-rate material has a higher scratch count. Thus, it is considered that material polished from the retainer ring is the sauce of scratches. However, the hardness of the ring materials is much lower than that of SiO<sub>2</sub>. Also, it is considered that the material from the retainer ring should not be large enough to create scratches because the surface of the ring appeared very smooth and no chipping was observed. In addition, if we note that there was no increase in the scratch count when a POU filter was applied, we cannot simply state that the polished material from the retainer ring was the sauce of microscratches.

Fig. 10. Microscratch count dependence on wear rate for different materials and ring pressures.

**Fig. 11.** (Color online) Optical microscopy and SEM images of accessory mark after tungsten plug CMP.

Providing that the retainer ring wear rate is proportional to the ring pressure, the wear rate for each ring pressure can be calculated. The graphs in Figs. 7 and 9 are merged in Fig. 10, placing the wear rate on the *x*-axis. The scratch counts under a high ring pressure are above the line of the material wear rate dependence. It also shows that the reason for the high ring pressure causing a higher scratch count is not solely the amount of material polished from the retainer ring.

The above results indicate the mechanism of the scratch count dependences on the ring pressure and material wear rate as follows. Polymers are polished from the retainer ring. The polished polymers react with large particles in the slurry. Polymers and particles agglomerate to create larger particles, which cause microscratches. This agglomeration is accelerated by the stress induced between the ring and the polishing pad. This is the reason why the scratch counts under a high ring pressure are above the line of the material wear rate dependence.

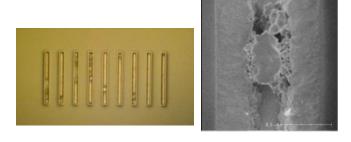

There is evidence to support the above model. During the introduction of tungsten CMP<sup>30,31)</sup> more than 10 years ago, there was an issue of accessory patterns being filled with foreign materials. In tungsten plug CMP, plug patterns are filled with tungsten, but accessory marks such as alignment marks were designed not to be fully filled with tungsten because it is necessary detect them after CMP. Therefore, foreign materials were easily filled there. Figure 11 shows accessory mark photographs after tungsten CMP. This filling caused the critical issue of upper layer explosion with degassing. This issue was observed only with the air-bagtype head. The backing-film-type head did not have the issue.

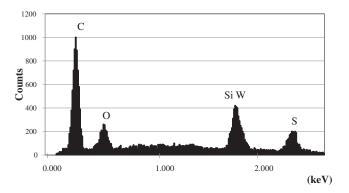

**Fig. 12.** EDX analysis of filling materials at accessory mark after tungsten CMP.

The difference in the retainer ring structure was considered to be the cause of the issue. The filling material was analyzed by EDX, and tungsten, silicon, oxygen, and sulfur atoms were detected, as shown in Fig. 12. Silicon and oxygen were considered to come from silica particles in the remaining slurry in the mark. Sulfur was considered to come from the retainer ring. At that time, the retainer ring was made of PPS, which included sulfur. No source other than the retainer ring was considered to be the source of sulfur. When the ring material was changed to SiC, which is very difficult to polished, the filling of the accessory mark was eliminated. This result indicates that polished polymers from the retainer ring can accelerate agglomeration with particles in the slurry.

The proposed model of the defect formation by the retainer ring is not considered to be a major cause of microscratches. It is a minor factor that accelerates defect formation only when other factors, such as slurry parameters, are under poor conditions. However, as device features continue to shrink and further defect reduction becomes more difficult, this model will help to minimize defects in CMP.

## 4. Conclusions

A strong correlation between the defect count and retainer ring pressure was found. This correlation is not related to changes in local pressure distribution at the wafer edge. It is considered that polished polymers from the retainer ring during CMP react with large particles in the slurry to make large agglomerates that cause microscratches. Lowering the ring pressure, which means the use of a new head structure that can control edge pressure distribution and wafer-holding capability with a low ring pressure, and applying materials that are difficult to polish can be a new approach to minimizing defects in CMP.

#### Acknowledgement

The authors would like to thank Mr. Shigeyuki Yoshida of

Renesus Electronics for providing his data of the foreign material filling issue in tungsten CMP.

- 1) A. Isobe: Proc. SEMI Technology Symp. Jpn., 1991, p. 276.

- M. Krishnan, J. W. Nalaskowski, and L. M. Cook: Chem. Rev. 110 (2010) 178.

- Y. Moon, R. Venigalla, C. Sheraw, C. Wang, J. Cummings, D. Canaperi, D. Lee, L. Hall, and L. Economikos: Proc. Int. Conf. Planarization/CMP Technol., 2009, p. 183.

- K. Wijekoon, R. Lin, B. Flankin, S. Yang, F. Redeker, G. Amico, and S. Nanjangud: Solid State Technol. 22 (1998) 53.

- 5) S.-Y. Kim and Y.-J. Seo: Microelectron. Eng. 60 (2002) 357.

- H.-P. Feng, J.-Y. Lin, M.-Y. Cheng, Y.-Y. Wang, and C.-C. Wan: J. Electrochem. Soc. 155 (2008) H21.

- 7) P. B. Zantye, A. Kumar, and A. K. Sikder: Mater. Sci. Eng. R 45 (2004) 89.

- 8) F. Preston: J. Soc. Glass Technol. 11 (1927) 127.

- K. Maeda, T. Kozuki, Y. Yamamoto, and S. Kadomura: Proc. Pacrim CMP, 2004, p. 43.

- T. H. Osterheld, S. Zuniga, S. Huey, P. McKeever, C. Garretson, B. Bonner, D. Bennett, and R. R. Jin: MRS Proc. 566 (1999) 63.

- 11) M. M. Touzov, T. Fujita, and T. K. Doy: Proc. ISSM, 2001, p. 337.

- Y.-R. Jeng, P.-Y. Huang, and W.-C. Pan: J. Electrochem. Soc. 150 (2003) G630.

- F.-C. Chang, S. Tanawade, and R. K. Singh: J. Electrochem. Soc. 156 (2009) H39.

- 14) A. K. Sikder, P. Zantye, S. Thagella, A. Kumar, B. M. Vinogradov, and N. V. Gitis: Proc. CMPMIC, 2003, p. 120.

- T.-Y. Kwon, B.-J. Cho, M. Ramachandran, A. A. Busnaina, and J.-G. Park: Tribology Lett. 50 (2013) 169.

- T. C. Chang, T. M. Tsai, P. T. Liu, C. W. Chen, S. T. Yan, H. Aoki, Y. C. Chang, and T. Y. Tseng: Thin Solid Films 447–448 (2004) 524.

- C. L. Borst, D. G. Thakurta, W. N. Gill, and R. J. Gutmann: Trans. ASME 124 (2002) 362.

- K. Jami, S. Vedula, G. Blumenstock, J. Chen, K. Kim, and Y. Kim: Solid State Technol. 52 (2009) 10.

- S. Kamo, H. Miyauchi, and H. Shida: Proc. Int. Conf. Planarization/CMP Technol., 2009, p. 271.

- 20) Y.-J. Seo, S.-Y. Kim, and W.-S. Lee: Microelectron. Eng. 65 (2003) 371.

- Z. Lin, J. Zahka, and G. Vasilopoulos: Tech. Rep. Millipore Corp. (Billerica, MA, 1998) MA071.

- E. E. Remsen, S. Anjur, D. Boldridge, M. Kamiti, S. Li, T. Johns, C. Dowell, J. Kasthurirangan, and P. Feeney: J. Electrochem. Soc. 153 (2006) G453.

- 23) Y.-J. Seo, S.-Y. Kim, Y.-O. Choi, Y.-T. Oh, and W.-S. Lee: Mater. Lett. 58 (2004) 2091.

- K. Tamai, T. Akatsuka, H. Morinaga, T. Doi, and S. Kurokawa: Proc. Int. Conf. Planarization/CMP Technol., 2009, p. 288.

- 25) G. B. Basim and B. M. Moudgil: J. Colloid Interface Sci. 256 (2002) 137.

- N. C. Crawford, S. Kim, R. Williams, D. Boldbridge, and M. W. Liberatore: Rheol. Acta 51 (2012) 637.

- A. Isobe, A. Yamane, K. Tanaka, S. Yamada, and M. Numoto: Proc. 8th CMPMIC, 2003, p. 509.

- 28) S. Kondo, S. Tokitoh, B. U. Yoon, A. Namiki, A. Sone, N. Ohashi, K. Misawa, S. Sone, H. J. Shin, T. Yoshie, K. Yoneda, M. Shimada, S. Ogawa, I. Matsumoto, and N. Kobayashi: Proc. IEEE Int. Interconnect Technology Conf., 2003, p. 86.

- S. Takemiya, N. Nakazawa, and S. Shinmaru: Reports Res. Lab. Asahi Glass Co., Ltd. 56 (2006) 29.

- W.-S. Lee, S.-Y. Kim, Y.-J. Seo, and J.-K. Lee: J. Mater. Sci.: Mater. Electron. 12 (2001) 63.

- K. Wijekoon, F. Redekar, G. Amico, and S. Nanjangud: Solid State Technol. 4 (1998) 53.